システムバス動作解析

- ピン配置の確認

- 外部ROMの選択の仕組みの確認

- ROM領域でもライトができるか

ということを検証するため、下記のようなプログラムを実行し、ロジアナでピンの動作を観察しました。割り込みをすべて禁止した上で、外部ROMを選択し、外部ROMに割り当てられるアドレス0x8000以降をひたすら読み書きするプログラムです。DIでIO(0x17)の割り込みも禁止されるのか不明なので、ねんのためそちらも禁止します。

のちほどわかったことには、UART通信を平行して行っている際にここでDI/EIをしてしまうと通信に不具合が出ます。 一方でDI/EIを挟まなくても外付けRAMの読み書きに問題は出ませんでした。

ORG 0x100

DI

IN A,(0x17)

PUSH AF

LD A,0x00

OUT (0x17),A ; DISABLE INTERURPTS

IN A, (0x19)

PUSH AF

LD B, 0x50 ; /CEROM2=L, BANK1=0, BANK0=1

OR B

OUT (0x19),A

; wait 10 seconds

LD B,0x10

A_LOOP:

CALL WAIT_FFFF

DEC B

JR NZ, A_LOOP

JP EXIT

WAIT_FFFF:

; count 0xFFFF

LD H,0xff

H_LOOP:

LD L,0xff

L_LOOP:

LD A,(0x8000) ; read ROM

LD A,(0x8001) ; read ROM

LD A,(0x8002) ; read ROM

LD A,(0x8003) ; read ROM

LD A,(0x8004) ; read ROM

LD A,(0x8005) ; read ROM

LD A,(0x8006) ; read ROM

LD A,(0x8007) ; read ROM

LD (0x8000),A ; write ROM

LD (0x8001),A ; write ROM

LD (0x8002),A ; write ROM

LD (0x8003),A ; write ROM

LD (0x8004),A ; write ROM

LD (0x8005),A ; write ROM

LD (0x8006),A ; write ROM

LD (0x8007),A ; write ROM

DEC L

JR NZ, L_LOOP

DEC H

JR NZ, H_LOOP

RET

EXIT:

POP AF

OUT (0x19),A ;RESUME ROM port

POP AF

OUT (0x17),A ; RESUME INTERRUPTS

EI

RET

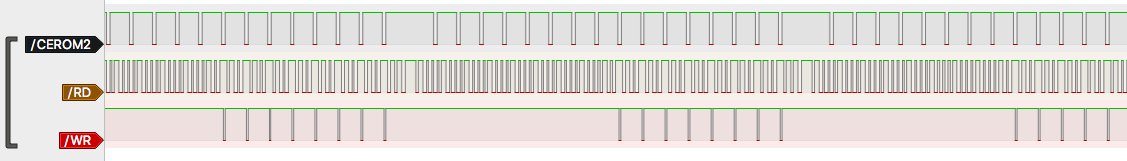

ロジアナの波形は下記でした。本当はもっとチャネル数の多いロジアナでアドレスとともに見たいところですが、手持ちのロジアナが8chなので、CEROM2/RD/WRを観察しました。

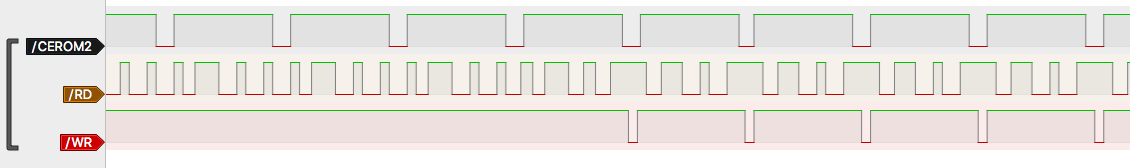

CEROM2が定期的に選択されている様子と、8回ずつのWRの繰り返しが見られます。RDは内蔵ROM/RAMに対するものが混在していて見にくいですが、ズームしてみると、

となっており、CEROM2=Lに対応するRD=LとWR=Lの繰り返しパターンが観察できました。良さそうですね。

こちらにZ80のマシンサイクルについての説明がありますが、この場合CEROM2=LになっているのがM2あるいはM3サイクルということのようです。